第一个台积nm!AMD Zen6架构CPU效能大增

发布时间:2026-04-19 来源:斑驳陆离网作者:quanlian

快科�日消息,近日,AMD公�年第三季财报,不仅交出亮眼的营收成绩单,AMD苏姿丰博士更亲自证实,其采用最先nm程技术、代号为Venice(威尼斯)的第六代AMD EPYC(霄龙)处理器正按计划进行,将如期�年正式发布。

苏姿丰在财报会议中重申,下一代EPYC威尼斯系列处理器将采用台积nm制程技术,并搭载Zen 6架构。

她确认,威尼斯芯片目前已进入实验室阶段,表现极佳。 相较于前一代的Zen 5架构的都灵CPU,威尼斯在性能、效率与运算密度上达到了实质性的成长。

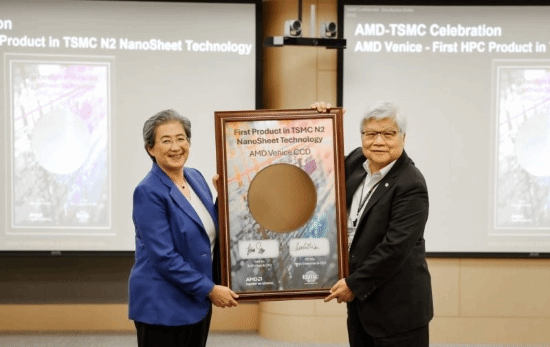

今月份,AMD正式宣布,代号为Venice(威尼斯)的第六代AMD EPYC(霄龙)处理器成为业界首款完成流片(tape out),并采用台积电先nm(N2)制程技术的高效能运算(HPC)产品。

现场,苏姿丰与台积电董事长兼总裁魏哲家一起手持Venice CCD,共同宣布了里程碑的一刻。

AMD表示,Venice预计将�年如期上市,有望早于传统使用台积电最新节点用户的苹果。

台积电的N2制程是首个依赖全环绕栅极 (GAA) 纳米片晶体管的工艺技术。恒定电压下可将功耗降低 24%、35%,性能提�%,同时与上一代 N3(3nm级)相比,晶体管密度提.15倍。

- 上一篇:{loop type="arclist" row=1 }{$vo.title}